# Mixed Signal Power Manager (MPM) for SmartFusion Reference Design

# **Reference Design Features**

# Monitor, Control, and Trim Power Supplies

- Includes complete FPGA design project, complete C source code for firmware, and standalone GUI tool for configuration

- Simultaneously monitor up to 32 power supplies

- Up to 32 user-defined digital output signals

- Up to 8 analog outputs

## **Power Supply Margin and Trimming**

- Trim and margin up to 8 power supplies in open loop (static) or closed-loop (dynamic) trimming modes

- Trimming configurable via I<sup>2</sup>C peek/poke or JTAG

- Independent digital closed-loop trim function for each trimmed regulator rail via pulse width modulation (PWM)

### Data Logging

- Critical events with timestamp stored in nonvolatile memory

- Real-time logging readable via I<sup>2</sup>C

# Filters, Flags, and Control Signals

- User configurable exponential decay averaging filtering

- Per channel hysteresis and glitch filtering

- 5 user configurable thresholds defining 6 conditions per channel: OFF, UV2, UV1, NOMINAL, OV1, OV2

- 32 general purpose digital output control signals

- User-defined digital inputs

- Digital output signals definable via AND/OR combination of inputs and internal flags

- Inverted or tristate buffered

- User configurable initial state (high, low, or highimpedance)

### Easy Power Sequencing

- 16 power sequence slots sequenced channels are assignable to any slot, or no slot for independent power-up

- User configurable per channel in-slot start-up delay, shut-down delay, nominal voltage, and timeout

- Power-off sequencing configurable as forward, reverse, or simultaneous

## JTAG and I<sup>2</sup>C Interface

In-system configurable via JTAG or single-channel slave mode I<sup>2</sup>C

# **Key MPM Benefits**

- Configurable power management in a low power, high reliability, flash-based SmartFusion intelligent mixed signal FPGA

- Full capabilities of hard 100 MHz 32-bit ARM<sup>®</sup>

Cortex<sup>™</sup>-M3 processor and associated communications

peripherals available for additional functionality on your

system

- More capability than non-reconfigurable discrete ASSP power management solutions

- Delivers Actel true flash advantages: nonvolatile, live at power-up, low power, immune to single-event upsets (SEU)

- Single-chip low power products simplify board design

- Low-power flash FPGAs reduce thermal management and cooling needs

- Proven in hardware

- Mixed Signal Power Manager Daughter Card (MPM-DC-KIT) connects to either the SmartFusion Evaluation Kit (A2F-EVAL-KIT) or SmartFusion Development Kit (A2F-DEV-KIT)

# **SmartFusion Device Features**

# On-Chip ARM Cortex-M3 Processor and Microcontroller Subsystem

- Hard 100 MHz 32-bit ARM Cortex-M3

- 1.25 DMIPS/MHz from zero wait state memory

- Memory protection unit (MPU)

- Single cycle multiplication, hardware divide

- JTAG debug (4 wires), Serial Wire Debug (SWD, 2 wires), and Single Wire Viewer (SWV) Interfaces

- · Internal memory

- Up to 512 Kbytes embedded nonvolatile flash memory (eNVM)

- Up to 64 Kbytes embedded high-speed SRAM (eSRAM)

- Multi-layer AHB communications matrix with up to 16 Gbps throughput

- 10/100 Ethernet MAC with RMII interface

- Programmable external memory controller supporting:

- Asynchronous Memories

- NOR Flash, SRAM, PSRAM

- Synchronous SRAMs

- Two each: SPI, I<sup>2</sup>C, UART, 32-bit timers

# High Reliability Flash-Based FPGA Fabric for Custom Control Logic

Up to 500,000 low power flash-based FPGA system gates available for custom digital extensions

#### On-Chip Clock Support

- 32 KHz to 20 MHz main oscillator

- Battery-backed 32 KHz low power oscillator with realtime counter (RTC)

- 100 MHz Embedded RC oscillator; 1% accurate

- Embedded analog PLL with 4 output phases (0, 90, 180, 270)

#### Analog Input Monitoring

- 12/10/8-bit mode ADCs with 500/550/600 Ksps sampling rate

- Internal 2.56 V reference or optional external reference

- One first-order ΣΔ DAC (sigma-delta) per ADC

- 12-bit 500 Ksps Update Rate

- Up to 5 high-performance analog signal conditioning blocks (SCB), each including:

- Two high-voltage bipolar voltage monitors (with 4 input ranges from ±2.5 V to -11.5/+14 V) with 1% accuracy

- High gain current monitor, differential Gain = 50, up to 14 V common mode

- Temperature monitor (resolution = 0.25°C in 12-bit mode; accurate from –55°C to 150°C)

- Up to 10 high-speed voltage comparators (15 ns tpd)

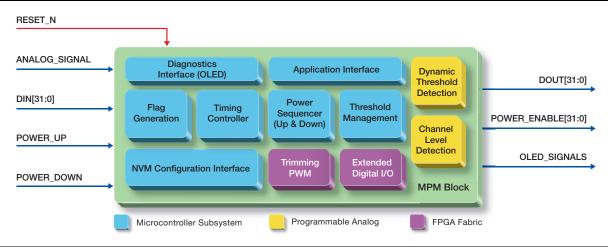

Figure 1 • MPM Implementation in SmartFusion Device

# **Description**

Actel's Mixed Signal Power Manager for SmartFusion design the reference leverages aroundbreaking SmartFusion intelligent mixed signal FPGA to deliver superior power monitoring, power sequencing, closed-loop trimming, and user configurable data and event logging of up to 32 external power supplies. You do not need to open any FPGA design tools to configure power supply sequencing, levels, or thresholds; the MPM for SmartFusion reference design can be programmed into the SmartFusion device through an easy-to-use standalone graphical user interface tool running on a PC. The MPM GUI tool enables you to configure power management for up to 32 external power supplies, configure open- or closed-loop voltage trimming for up to 8 power regulators, and drive output signals based on monitored voltages meeting or deviating from user-programmed operating limits, all without reprogramming the FPGA fabric. For experienced designers, the MPM for SmartFusion reference design includes a complete FPGA design project, complete C source code for the firmware, and comprehensive design documentation for use as the basis of your customized power management implementation.

MPM for SmartFusion reduces total parts count at the board level, increases system reliability by eliminating single points of failure, and delivers highly configurable, integrated power management.

Using the MPM GUI, you can configure all MPM input and output requirements by writing values to the SmartFusion device's on-chip embedded nonvolatile flash memory (NVM) via JTAG or I<sup>2</sup>C interfaces. These settings can be quickly altered and reloaded from the GUI or directly via register peek/poke using I<sup>2</sup>C, allowing rapid validation in functional hardware without the risk of altering FPGA circuitry.

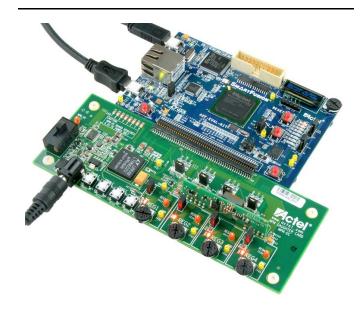

The MPM for SmartFusion Reference Design brings MPM to your bench using the four regulators on the MPM Daughter Card connected to either the *SmartFusion Evaluation Kit* or

the *SmartFusion Development Kit.* These four regulators function as an independent power supply subsystem controlled by MPM for SmartFusion. Additional regulator control channels and digital I/Os can be accessed for benchtop development via available mixed signal or digital headers.

The MPM for SmartFusion documentation and reference design are downloadable at http://www.actel.com/products/solutions/powermgt/default.aspx. You can view a 35 minute webcast on MPM for SmartFusion at http://www.actel.com/support/webcasts/default.aspx?f=MPM. More videos are available on Actel's YouTube channel, http://www.youtube.com/actelcorp.

Figure 2 • Mixed Signal Power Manager Daughter Card Kit (MPM-DC-KIT) connected to SmartFusion Evaluation Kit (A2F-EVAL-KIT)